## РОССИЙСКАЯ АКАДЕМИЯ НАУК

СИБИРСКОЕ ОТДЕЛЕНИЕ

# **АВТОМЕТРИЯ**

Nº 3

1993

УДК 681.31:535

### Б. Н. Панков

(Новосибирск)

#### ПАРАЛЛЕЛЬНАЯ ФОТОМАТРИЧНАЯ БИС С ЛОГИЧЕСКОЙ ОБРАБОТКОЙ СТРАНИЦ ДАННЫХ

Рассматривается новый подход к построению параллельных специализированных фотоматричных БИС, выполняемых с использованием МДП-технологии и обеспечивающих не только прием, фотоэлектрическое преобразование, накопление логических сигналов, но и их параллельную логико-арифметическую обработку. Сообщается о результатах разработки новой фотоматричной БИС ФМАЗУ для реализации параллельных методов поиска данных в страничноорганизованной оптической памяти. В БИС удачно сочетаются высокие скорости фотоэлектрического преобразования оптических страниц данных и их параллельной обработки с сохранением высокой надежности и помехоустойчивости фотоэлектрического преобразования в условиях потока данных, разброса оптических параметров изображений страниц, светового фона, неоднородностей электрофизических параметров по кристаллу фотоэлектронной БИС, а также неоднородностей, вносимых технологией производства БИС.

Развитие технологии страничной оптической памяти [1—4], создание на ее основе дисковых поисковых систем требуют разработки и применения новых матричных фотоприемных устройств, обеспечивающих не только прием, фотоэлектрическое преобразование, накопление логических сигналов, но и их параллельную логико-арифметическую обработку.

Известны примеры таких устройств. Так, фотоматричное ассоциативное ЗУ (ФМАЗУ) [5,6] обеспечивает фотоэлектрическое преобразование и чтение изображений страниц, восстанавливаемых из микроголограмм, параллельную логическую обработку данных, ввод «электрических» эталонов для сравнения и вывод полученных результатов через внешний интерфейс и скоростной контроллер в ЭВМ. Недостаток ФМАЗУ — сравнительно низкая чувствительность и помехозащищенность фотоэлектрических преобразователей «свет—код» (~10<sup>-11</sup> Дж/эл.). Это приводит к необходимости значительного увеличения времени накопления оптических сигналов, что практически на нет сводит преимущества ФМАЗУ при параллельной обработке сигналов либо требует существенного увеличения световой мощности при выборке информации из оптической памяти.

В настоящей работе предлагается перспективный подход к построению параллельных специализированных фотоматричных БИС, выполняемых с использованием МДП-технологии, и сообщается о результатах разработки новой фотоматричной БИС ФМАЗУ, обеспечивающей параллельное фото-электрическое преобразование оптической страницы данных, содержащей  $N1 \times N2$  информационных элементов (бит) и ее последующее чтение по словам или логическую обработку за один рабочий такт БИС. ФМАЗУ ориентировано на реализацию параллельных методов поиска данных. В такой БИС высокая скорость фотоэлектрического преобразования оптических страниц данных хорошо согласуется с высокой скоростью их обработки, сохраняется высокая надежность и помехоустойчивость фотоэлектрического преобразования в условиях непрерывного потока данных, обеспечивается компенсация светового фона, неоднородностей электрофизических парамет-

ров по кристаллу БИС, а также неоднородностей, вносимых технологией производства БИС.

Остановимся на нескольких особенностях построения фотоматричной БИС с параллельным оптическим входом и параллельной обработкой данных.

1. Применение в каждой элементарной ячейке БИС преобразователей «свет—код» с дифференциальными фоточувствительными входами.

Как известно [7], при использовании такого фотоэлектрического преобразователя информация на оптической странице памяти записывается в парафазном коде, так что при восстановлении страницы данных на фоточувствительные входы каждой ячейки одновременно проецируются оптические нули и единицы. Будучи избыточным, парафазное кодирование по данным [8] позволяет, с одной стороны, стабилизировать режим записи изображений страниц данных на оптическом носителе, а с другой — улучшить условия их

фотоэлектрического преобразования и чтения.

Основными элементами фотоприемной ячейки (ФПЯ) БИС в этом случае является дифференциальный усилитель с фотодетекторами на его входах, работающими в режиме накопления оптических сигналов [7, 9], т. е. дифференциальный фотоэлектрический преобразователь (ДФЭП). Применение таких элементов позволяет повысить чувствительность фотоэлектрического преобразователя и его устойчивость к оптическим и электрическим помехам. Так, в этом случае обеспечивается устойчивое пороговое фотоэлектрическое преобразование страниц в условиях низкого контраста оптических единиц и нулей, сильного изменения контраста от страницы к странице и наличия переменного светового фона. По данным [10] применение в голографической памяти парафазного кодирования в сочетании с использованием дифференциального фотоэлектрического преобразователя повышает на несколько порядков достоверность фотоэлектрического преобразования данных.

На наш взгляд, применение парафазного кодирования оптических сигналов и их последующий дифференциальный фотоприем также весьма перспективны при создании 3-D интегральных микросхем с оптическими

межсоединениями [11].

2. Совмещение во времени выполнения в фотоприемной ячейке основных времяемких операций: фотоэлектрического преобразования оптических сигналов, их накопления, адресной выборки, логической обработки и т. п.

Для этого необходимо предусматривать на уровне элементарной фотоприемной ячейки отдельно функционирующую фотоприемную часть (дифференциальный фотоэлектрический преобразователь) и, по крайней мере, один элемент памяти, в которую заносятся результаты фотоэлектрического преобразования и на уровне которой затем в БИС выполняются все необходимые операции со страницей данных. Упомянутое выше совмещение операций позволит организовать с помощью фотоматричной БИС конвейер по накоплению и обработке потока данных, поступающих из оптической памяти, при котором во время накопления текущей страницы производится необходимая обработка или вывод данных предыдущей страницы.

3. Подавление влияния как неоднородностей и нестабильностей электрофизических параметров полупроводникового кристалла БИС, так и неоднородностей, вносимых технологией производства (здесь имеются в виду такие негативные факторы, от которых не спасает дифференциальный фотоприем).

Основной фактор (кроме несимметрии параметров фотоприемников в ячейке), вызывающий разброс и ограничение дифференциальной фоточувствительности ДФЭП, — это начальный разбаланс используемого в ДФЭП дифференциального усилителя. Как известно [7, 9], начальный разбаланс дифференциального усилителя возникает из-за несимметрии параметров его элементов и, суммируясь с полезным сигналом на выходе ДФЭП, напрямую ограничивает пороговую чувствительность ДФЭП. Анализ показывает, что необходимость в балансировке дифференциального усилителя или в учете его начального разбаланса, вызванного характерными для современных МДП-технологий [12] разбросами таких параметров МДП-транзисторов, как пороговое напряжение усилительных и нагрузочных транзисторов, крутизна их

характеристик и других параметров элементов дифференциального каскада, появляется при стремлении к обеспечению высокой чувствительности (~10<sup>-11</sup> Дж/эл, и выше) и к минимальному разбросу характеристик элементарных ячеек БИС в условиях сравнительно большого размера кристалла (~10 × 10 мм и более) БИС при наличии в ней нескольких десятков тысяч

элементов (МДП-транзисторов, фотодетекторов, конденсаторов) [12, 13]. Нами предложено и разработано несколько вариантов схем ДФЭП [14— 17], которые содержат устройства автоматической балансировки или учета начального разбаланса дифференциального каскада ДФЭП на каждом рабочем такте ДФЭП, в том числе с разделенными фотодиодами [14], запоминающими конденсаторами [15, 16 [н с использованием отрицательной обратной связи [17].

4. Размещение интерфейса, посредством которого матрица фотоприемных яческ должна взаимодействовать через свои внешние шины с контроллерами и внешними ЭВМ, на кристалле по периферии матрицы из  $N1 \times N2$  элемен-

тарных фотоприемных ячеек.

Такие возможности уже реализуются в фотоэлектрических преобразователях изображений на ПЗС, самосканируемых фотодиодных линейках, динамической полупроводниковой памяти и др. [18]. Однако в известных фотоматричных БИС интерфейсные устройства отсутствуют, и поэтому связь с контроллерами обеспечивается с помощью весьма громоздкого внешнего интерфейса [19], что снижает их быстродействие и помехоустойчивость, усложняет их применение.

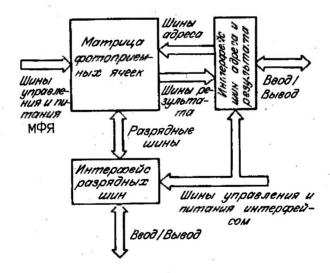

Структурная схема предлагаемой фотоэлектронной БИС ФМАЗУ, разра-

ботанной с учетом изложенных выше соображений, приведена на рис. 1.

Данное ФМАЗУ представляет собой фотоматричный процессор, имеющий параллельный оптический вход и реализующий параллельный ассоциативный поиск и выборку данных в пределах страницы  $K = \{k_{ln}\}$  странично-организованной голографической памяти. По сравнению с [6, 7] ФМАЗУ имеет раздельные уровни по вводу и обработке данных. На одном уровне осуществляется дифференциальный прием и накопление данных, а на другом — их хранение, параллельная логическая обработка и выборка. В структуре ФМАЗУ имеется также интерфейс, посредством которого осуществляется взаимодействие ФМАЗУ с контроллерами.

Базисной функцией, реализуемой ФМАЗУ параллельно в процессе обработки в пределах страницы, загружаемой в ФМАЗУ по параллельному оптиче-

Puc. I

скому входу, является вектор-функция  $R = \{r_i\}$ :

$$r_i = \sum_{n \in (M \neq 0)} (k_{ln} Z_n + k_{ln} \overline{Z}_n)$$

либо

$$r_i = \sum_{n \in (M \neq 0)} (k_{in} \overline{Z}_n + \overline{k}_{in} Z_n),$$

где Z-n-и разряд двоичного кода поискового аргумента, поступающего в ФМАЗУ по электронному входу;  $k_n-n$ -й разряд двоичного слова с номером l, записанного в ФМАЗУ. Суммирование определяется как дизъюнкция и берется по всем незамаскированным разрядам, для которых  $M \neq 0$ . При этом индицируется совпадение (с точностью до замаскированных разрядов) поискового аргумента и слова, хранящегося в ФМАЗУ.

ФМАЗУ по рис. 1 содержит матрицу (решетку) однородных по структуре фотоприемных ячеек (МФЯ), связанных между собой и интерфейсом, расположенным по периферии МФЯ, системой ортогональных шин.

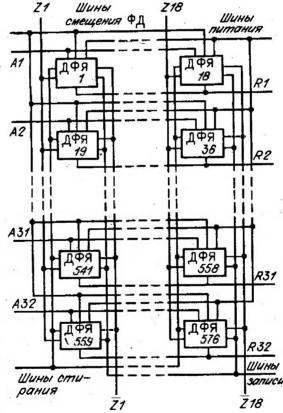

Структурная схема МФЯ ФМАЗУ приведена на рис. 2, где Z и  $\overline{Z}$  — разрядные шины, A — шины адреса A и R — шины результата. На рисунке показаны также общие для всех ячеек шины питания, шины смещения фотодиодов и управления (шины стирания и шины записи). Матрица фотоприемных ячеек ФМАЗУ содержит  $32 \times 18$  дифференциальных фотоприемных ячеек, имеет 32 строки (соответственно 32 шины адреса A и 32 шины результата R) и 18 столбцов дифференциальных фотоприемных ячеек (18 разрядов, соответственно 36 разрядных шин Z и Z).

По адресным шинам A осуществляется адресное обращение по строкам к содержимому ячеек памяти при выводе содержимого на разрядные шины Z и Z при чтении данных. На шины результата R выводится результат логического сравнения слова опроса, подаваемого на разрядные шины Z и Z, со словами-признаками, разряды которых хранятся в ячейках памяти МФЯ.

ФМАЗУ взаимодействует с контроллерами и внешними ЭВМ через интерфейсы разрядных шин МФЯ, шин адреса и результата поиска.

Рассмотрим возможные схемы выполнения интерфейса ФМАЗУ, которые могут отличаться по количеству внешних шин ФМАЗУ и направлению передачи информации по этим шинам (ввод или вывод по отношению к ФМАЗУ).

Интерфейс разрядных шин. Как уже отмечалось, разрядные шины Z и  $\overline{Z}$  являются двунаправленными. По этим шинам информация выводится с ФМАЗУ при адресной выбор-

Puc. 2

ке и по ним же передается во ФМАЗУ при выполнении сравнения. Возможны следующие решения:

1. Внешние шины ввода/вывода интерфейса могут быть однонаправленными. В этом случае шины ввода (шины опроса) могут быть парафазными и однофазными. При парафазных шинах ввода/вывода их число равно удвоенному количеству разрядов МФЯ, а операция маскирования соответствующего разряда слова опроса производится за счет модификации кода опроса этого разряда, т. е. ключ и маска передаются на ФМАЗУ одновременно. Для однофазных шин ввода/вывода их число равно количеству разрядов, а передача ключа и маски по ним осуществляется разновременно.

2. Внешние шины ввода/вывода интерфейса могут быть двунаправленными и однофазными с разновременной передачей разрядов ключа и маски. Это решение отличается минимальным числом шин ввода/вывода. Возможно также сочетание двунаправленных шин ввода/вывода и однонаправленных шин маски. В этом случае ключ и маска передаются на вход интерфейса

одновременно.

Интерфейс шин адреса и результата.

1. Внешние шины адреса и результата интерфейсного устройства могут быть однонаправленными. В этом случае интерфейс может быть выполнен в виде дешифратора адреса и мультиплексора шин результата или в виде сдвигового регистра адреса.

2. Внешние шины адреса и результата интерфейсного устройства могут быть двунаправленными. Возможные решения со сложным интерфейсом, размещенным на периферии кристалла МФЯ и обеспечивающим обработку многоразрядного результата сравнения за несколько тактов, здесь не рассматриваются.

Не останавливаясь подробно на анализе достоинств и недостатков возможных структур интерфейса и их схемной реализации (интерфейсы отличаются производительностью, а конструктивно отличаются количеством внешних шин ФМАЗУ и направлением передачи информации по этим шинам), укажем только на наиболее приемлемый в реализации и по производительности интерфейс ФМАЗУ. В нем интерфейс разрядных шин имеет на выходе двунаправленные шины ввода/вывода с разновременной передачей ключа и маски, а на

Puc. 3

выходе интерфейса шин адреса и результата имеются также двунаправленные шины адреса/результата. При этом предусматривается разновременная передача ключа и маски запроса — «электрического» эталона при операции сравнения — по шине ввода/вывода ФМАЗУ (сначала в интерфейсное устройство разрядных шин заносится ключ, а передача маски на ФМАЗУ производится при операции сравнения).

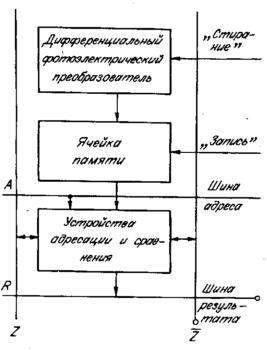

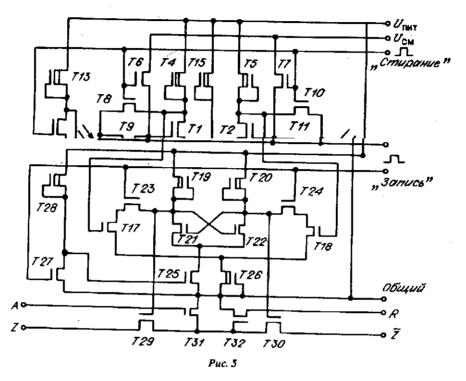

Структурная схема дифференциальной фотоприемной ячейки ФМАЗУ приведена на рис. 3. Схема содержит следующие основные функциональные элементы: дифференциальный фотоэлектрический преобразователь (ДФЭП), ячейку памяти (ЯП), устройства адресации и сравнения, информационные и управляющие шины.

ДФЭП осуществляет фотоэлектрическое преобразование двух оптических сигналов и сравнение (вычитание) их по энергиям за время накопления. Результатом преобразования является аналоговый электрический сигнал (напряжение), знак и амплитуда которого определяются разностью между световыми энергиями оптических сигналов, попадающих на входы фотоприемников (фотодиодов) ДФЭП за время интегрирования (накопления), измеряемое от конца импульса стирания до момента отсчета выходного сигнала.

ДФЭП функционирует независимо от остальных функциональных элементов ФПЯ и содержит дифференциальный усилитель (ДУ) с фотоприемниками на входе [7].

Puc. 4

Фотоприемники в ДФЭП представляют собой фотодиоды, которые образованы p-n-переходами между диффузионными областями МДП-транзисторов (истоками или стоками) и подложкой и подключены к затворам усилительных транзисторов ДУ и через ключевые транзисторы к источнику напряжения смещения фотодиодов. Управляются ключевые транзисторы стирания по затворам, подключенным к шине стирания, сигналом стирания.

Следующий функциональный элемент — ячейка памяти — представляет собой выходной каскад с функциями высокочувствительного компаратора с ячейкой памяти (триггер-защелки) [20]. Этот элемент осуществляет нормирование по уровню выходного сигнала ДФЭП, его запись в ячейку памяти (триггер) и последующее хранение.

Запись информации в ячейку памяти с выхода ДФЭП производится по заднему фронту импульса записи. При этом хранение информации в ЯП осуществляется независимо от выходного сигнала ДФЭП и может быть нарушено только в момент прохождения сигнала записи.

Управление записью в ячейке памяти производится только от шины записи. Таким путем в ФПЯ осуществляются совмещение во времени операций накопления разности сравнираемых оптических сигналов на текущем такте и хрансние результатов накопления, полученных на предыдущем такте.

Взаимодействие дифференциальной фотоприемной ячейки с информационными шинами МФЯ (разрядными, адреса и результата) осуществляется через устройства адресации и сравнения, связывающие указанные шины с информационными выходами ФПЯ, которыми в данной структуре ФМАЗУ являются выходы ячейки памяти.

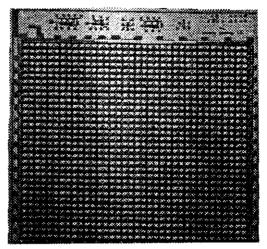

В экспериментальных образцах ФМАЗУ размерностью  $32 \times 18$  дифференциальных фотоячеек, изготовленных по n-канальной МДП-технологии с поликремниевым затвором и двумя типами n-канальных МДП-транзисторов, элементарные ячейки МФЯ реализованы с использованием ДФЭП с разделенными фотодиодами [14]. Вид кристалла ФМАЗУ показан на рис. 4.

Электрическая схема ячейки экспериментальных образцов со структурой по рис. 3 приведена на рис. 5. При этом МДП-транзисторы T1-T16 с фотодиодами  $\PhiД1-\PhiД4$  входят в состав ДФЭП ячейки, транзисторы T17-T28 — в используемую в ней триггер-защелку, а транзисторы T29-T32 — в устройство адресации и сравнения [16].

ДФЭП ячейки содержит дифференциальный усилитель с усилительными (T1, T2) и нагрузочными (T4, T5) транзисторами. Транзисторы T3, T14—T16 составляют управляемый генератор тока дифференциального усилителя, обеспечивающий необходимый динамический диапазон парафазных оптических сигналов и постоянство дифференциальной фоточувствительности ДФЭП для сигналов с различными значениями контраста (расчетное

подавление фона составляет > 40 дБ) [16]. Ключевые транзисторы T8-T11 с инвертором стирания на транзисторах T12, T13 осуществляют начальную установку напряжений смещения на емкостях фотодиодов и автоматическое устранение начального разбаланса (балансировку) дифференциального усилителя на каждом рабочем такте ДФЭП.

Пары фотодиодов ФД1, ФД3 и ФД2, ФД4 образуют составные фотодиоды, используемые для приема сравниваемых ДФЭП оптических сигналов. Выполняются фотодиоды в парах примыкающими друг к другу. Причем отношения площадей S1/S2 основных (ФД1, ФД2) и вспомогательных (ФД3, ФД4) фотодиодов в парах выполнены в соответствии с условием автоматической балансировки дифференциального каскада при стирании [14]:

$$S1/S2 = K_{\pi} - 1,$$

где  $K_{\rm g}$  — полный дифференциальный коэффициент усиления усилителя. Расчетное значение S1/S2 для экспериментальных образцов ФМАЗУ равно 11.

Элемент памяти в фотоприемных ячейках (тригтер-защелка на транзисторах T17—T26) совмещает функции регенеративного компаратора выходного сигнала ДФЭП. Инвертор на транзисторах T27, T28 осуществляет в ячейке инверсию сигнала записи.

Интерфейс разрядных шин ФМАЗУ для организации взаимодействия с внешним контроллером ФМАЗУ по 18 двунаправленным шинам ввода/вывода содержит усилители считывания данных с буферными каскадами на три состояния, логические элементы управления разрядными шинами в различных режимах, а также управляемый регистр ключа.

Интерфейс шин адреса/результата обеспечивает возможность обращения от внешнего контроллера ФМАЗУ к одной из 32 адресных шин ФМАЗУ и вывод

32-разрядного результата сравнения на 32 двунаправленные шины адреа/результата и содержит логические устройства управления шинами в различных режимах.

Исследования партии экспериментальных образцов ФМАЗУ показали, что при мощности оптического сигнала  $\sim 5 \cdot 10^{-8}$  Вт/бит фоточувствительность элементарных ячеек ФМАЗУ (не хуже  $\sim 10^{-13}$  Дж/яч.) дает возможность получить скорость потока данных на оптическом входе ФМАЗУ  $\sim 100$  Мбит/с. При этом скорость логической обработки данных на странице в зависимости от вида обработки (поиска) может составлять от 100 Мбит/с до  $\sim 2,5$  Гбит/с.

Параллельная фотоматричная БИС с указанными выше характеристиками, помимо дисковой голографической памяти, может иметь и другие эффективные применения.

#### СПИСОК ЛИТЕРАТУРЫ

- 1. Твердохлеб П. Е. Голографическая память и информационные машины // Автометрия.—

1980.—№ 2

- Tverdokhleb P. E., Pankov B. N. Parallel associative VLSI processor with optical input // Proc. SPIE.—1990.—1230.—P. 662.

- Saton I., Kato M. Holographic disk recording of digital data with fringe stabilization // Appl. Opt.—1988.—27, N 14.—P. 2987.

- 4. Блок А. А., Домбровский В. А., Домбровский С. А. и др. Дисковая голографическая память // Автометрия.—1992.—№ 1.

- Кибирев С. Ф., Коняев С. И., Наймарк С. И. Фотоматричный ассоциативный накопитель // Автометрия. —1982. —№ 2.

- Коняев С. И. Фотоматричное ассоциативное запоминающее устройство // Электрон. пром-сть.—1988.—№ 4.

- 7. Наймарк С. И., Третьяков В. М. Фотоприемный интегральный матричный элемент для считывания парафазного оптического кода // Автометрия.—1977.—№ 2.

- Вербовецкий А. А., Федоров В. В. Запись на фазовые голограммы двоичной информации в парафазном коде // Оптика и спектроскопия. —1972.—33, вып. 6.

- 9. Наймарк С. И. Многоэлементные МДП-интегральные фотодиодные преобразователи оптических сигналов. Ч. 2. Оптоэлектронные функциональные преобразователи оптических сигналов. Устройства и системы на их основе // Обзоры по электрон. технике /ЦНИИ «Электроника». Сер. 3. Микроэлектроника.—1983.—Вып. 2 (937).

- 10. Домбровский В. А., Домбровский С. А., Пен Е. Ф. Помехоустойчивость голографической памяти при парафазном кодировании данных // Автометрия.—1989.—№ 2.

- Егоров В. М., Косцов Э. Г. Перспективы создания оптических цифровых высокопроизводительных вычислительных устройств // Автометрия.—1985.—№ 1.

- 12. Технология СБИС /Под ред. С. Зи. М.: Мир, 1986.

- 13. Мурога С. Системное проектирование сверхбольших интегральных схем. М.: Мир, 1985.

- А. с. 1619345 СССР. Фотоприемная ячейка /В. Е. Бутт, Б. Н. Панков, В. В. Савельев, П. Е. Твердохлеб.—Заявл. 06.02.89; Опубл. 07.01.91, Бюл. № 1.

- 15. А. с. 1619344 СССР. Фотоприемная ячейка /В. Е. Бутт, Б. Н. Панков, В. В. Савельев, П. Е. Твердохлеб.—Заявл. 10.02.89; Опубл. 07.01.91, Бюл. № 1.

- 16. А. с. 1709392 СССР. Ячейка фоточувствительного матричного запоминающего устройства /В. Е. Бутт, Б. Н. Панков, В. В. Савельев, П. Е. Твердохлеб.—Заявл. 30.10.89; Опубл. 30.01.92, Бюл. № 4.

- 17. А. с. 1626261 СССР. Фотоприемная ячейка /В. Е. Бутт, Б. Н. Панков, В. В. Савельев, П. Е. Твердохлеб.—Заявл. 17.02.89; Опубл. 07.02.91, Бюл. № 5.

- 18. Пат. 4096584 США. Low power/high speed RAM.—Заявл. 20.06.78.

- Бутт В. Е., Вьюхина Н. Н., Козик В. И. и др. Поиск соединений по фрагментам структурных формул в голографической памяти // Автомегрия. —1990. —№ 1.

- 20. Беломестных В. А., Касперович А. Н., Солоненко В. И. Компараторы на основе тригтер-защелки // Автометрия. —1975. —№ 1.

Поступила в редакцию 5 апреля 1993 г.