|

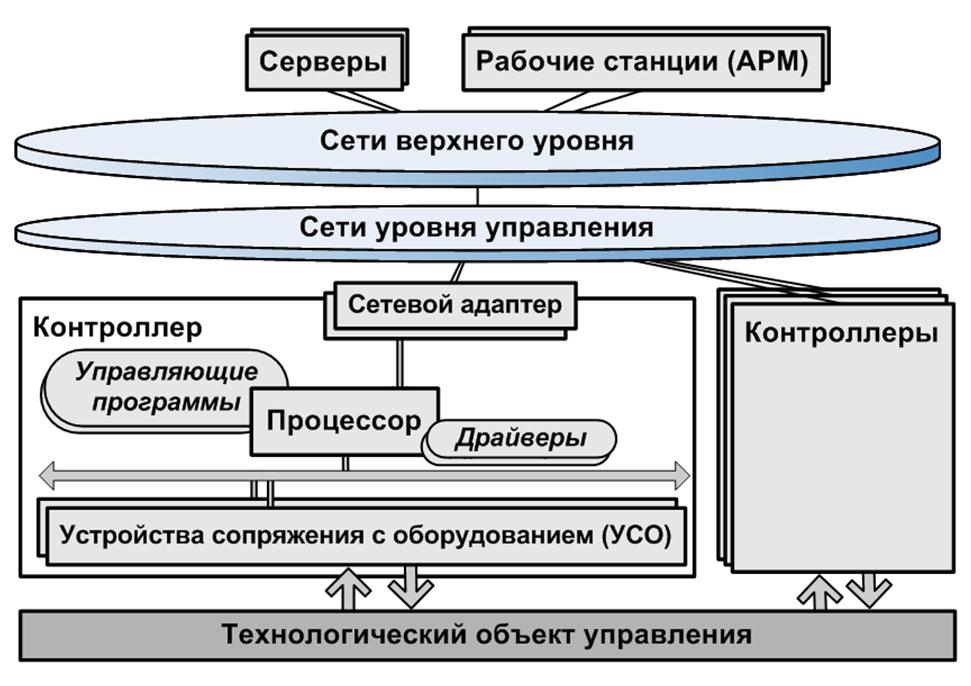

Рис. 1. Классическая многоуровневая архитектура системы управления

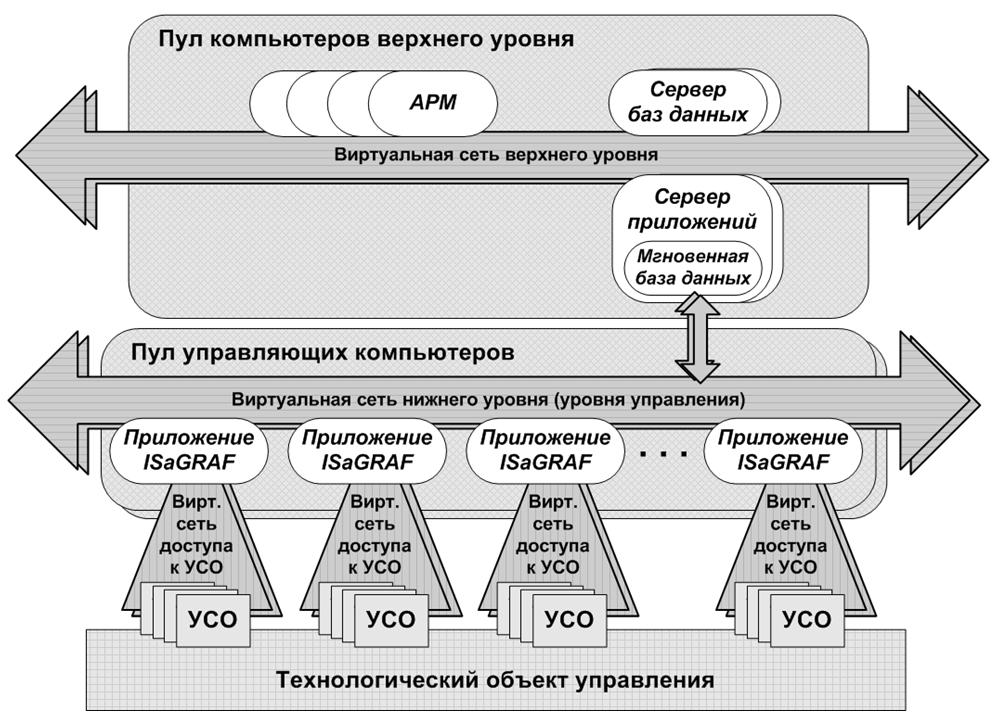

Рис 2. Организация одноранговой распределенной системы управления (ОРСУ)

Рис. 3. Перспективная архитектура АСУТП на базе ОРСУ

|

Проведено исследование существующих перспективных технологий и алгоритмов, которые можно использовать при создании высокопроизводительных надежных отказоустойчивых распределенных систем управления, выгодно отличающихся от систем управления с классической многоуровневой архитектурой (рис. 1).

Предложены и исследованы различные варианты организации единой программной среды и унифицированной процессорной платформы, позволяющих использовать в Управляющих Компьютерах (УК) любые процессорные ядра с масштабируемым аппаратным и программным окружением. Определены ключевые технологии и решения, которые предполагается использовать при построении одноранговых распределенных систем управления (ОРСУ) (рис. 2).

В результате проведенных исследований выбрано следующее решение: управляющий компьютер должен быть выполнен в виде платы-носителя процессорного модуля, в промышленном исполнении, конструктивно выполненной в стандарте EBX и содержащей набор современных интерфейсов для стыковки с внешними системами. В качестве процессорных модулей, устанавливаемых на плате-носителе, предполагается использовать серийно выпускаемые рядом производителей модули стандарта QSeven.

Архитектурное решение по разделению процессорной платформы на плату-носитель и процессорный модуль стандартизованного исполнения обеспечит замену процессорного модуля без изменения конструктива и состава платы-носителя, позволит использовать любую оптимальную для прикладной задачи процессорную архитектуру – x86, ARM, PPC, и, соответственно, любую из распространенных операционных систем (Windows, Android, Linux, QNX и пр.).

Процессорная платформа должна содержать в своем составе ряд современных высокопроизводительных интерфейсов (PCIe, miniPCIe, USB, SATA, miniSATA, Gigabit Ethernet, SD Card, LVDS, DVI, HDMI, VGA).

Наличие интерфейсов PCIe и miniPCIe обеспечит масштабируемость платформы за счет установки типовых карт расширения. Это могут быть как дополнительные коммуникационные интерфейсы (беспроводные Wi-Fi и 3G, проводной или оптический Ethernet), так и специализированные модули расширения для решения специфических задач автоматизации.

Вычислительная платформа должна обладать низким энергопотреблением (не более 20 Вт), что позволит использовать ее в системах с пассивным охлаждением повышенной надежности не требующих технического обслуживания на протяжении всего срока службы.

Использование единой программной среды и унифицированной процессорной платформы при развертывании программно-технических комплексов (ПТК) с архитектурой ОРСУ (рис. 3) позволит создавать гибкие и масштабируемые сложные системы автоматизации для транспорта, энергетики и других отраслей промышленности.

Публикации

- Нестуля Р.В., Сердюков О.В., Скворцов А.Н. Масштабируемая отказоустойчивая среда управления сложными технологическими объектами на основе одноранговой распределенной архитектуры // Автометрия, 2013, том 49, № 6. С. 70–78.

- Нестуля Р.В. Архитектура высокопроизводительной системы сбора и обработки данных для крупных распределенных телемеханических систем с высокими требованиями по надежности и отказоустойчивости // Сборник тезисов докладов Всероссийской конференции «Индустриальные информационные системы» ИИС-2013. Новосибирск, Академгородок, 24–28 сентября 2013 г. С. 47–48.

- Скворцов А.Н. Распределенная среда управления сложными объектами теплоэнергетики // Сборник тезисов докладов Всероссийской конференции «Индустриальные информационные системы» ИИС-2013. Новосибирск, Академгородок, 24–28 сентября 2013 г. С. 56-57.

- Нестуля Р.В., Сердюков О.В., Скворцов А.Н. Архитектура отказоустойчивой распределенной среды управления для АСУТП крупных технологических объектов // Труды Шестой Международной конференции «Параллельные вычисления и задачи управления PACO'2012», (Россия, Москва, 24–26 октября 2012 г.), т. I. С. 178-187.

|